検索

Contact

Qsysを利用した回路の使い方(メモリアクセス編)

Qsysを利用したFPGA回路をリファレンス制御アプリケーションから制御する方法(メモリ・アクセス編)

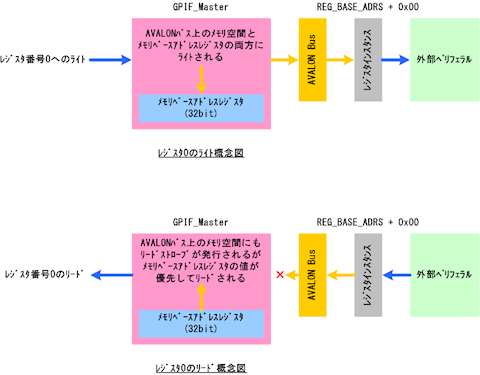

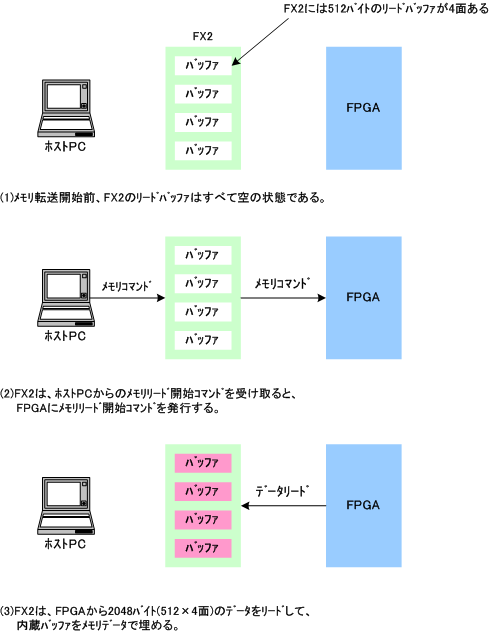

メモリアクセスは高速で大容量のデータ転送を行う時に使用する転送方法です。 GPIF-AVALONブリッジ回路によりAVALONバスのプロトコルに変換された後では、メモリアクセスとレジスタアクセスの本質的な違いはありません。 メモリアクセスは、GPIF-AVALONブリッジ・マスタ回路内にあるメモリベースアドレスレジスタを転送開始時のスタートアドレスとして使用します。 このメモリベースアドレスはレジスタ番号"0" に配置した32ビットのレジスタで、AVALONバス上にある「レジスタベースアドレス+0x00」のペリフェラルと重複して配置しています(サンプル回路では、"notuse"という名称のPIOペリフェラルにレジスタ番号"0"を割り当てています。ユーザが間違えてレジスタ"0"を使用しないためにに割り当てています)。 注意点は以下3点です。 『メモリ操作の手順』 ホストPCの制御アプリケーションからメモリ転送を行う手順を説明します。

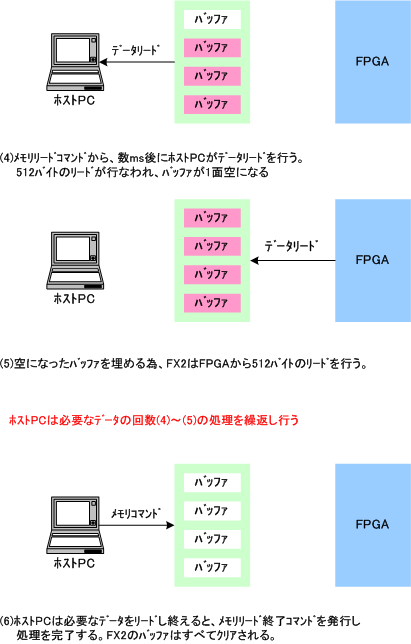

(補足) 『メモリ転送時の総転送バイト数』 メモリリードの場合、ホストPC上の制御アプリケーションで指定したメモリリードのデータ量と、実際にGPIF-AVALONブリッジ・マスタがペリフェラルから読み出すデータ量が異なります。 ホストPCがメモリリードを開始するとFX2とGPIF-AVALONブリッジ・マスタ内のFIFOは、ホストPCからUSBのリードパケット(データ転送要求)を受信後、即座にリードデータをホストPCに出力するため、FIFOを常にFullの状態にする様にペリフェラルからデータをリードしておきます。 「ホストPCが読み出すデータ量 = メモリリードで指定したデータ量 + 4096バイト」となります。

(※レジスタベースアドレスと物理メモリのアドレスを重複させる事で低速ではありますが、レジスタアクセスで物理メモリにアクセスする事も可能です。)

SX-USB3システム開発ボードのサンプル回路と同じマップ(下表)でメモリが配置されている場合です。

名称

先頭アドレス

終了アドレス

ssram1

0x00000000

0x007fffff

ssram2

0x00800000

0x00ffffff

レジスタ番号"0"に「0x00000000」をセット後に転送レングスを「0x01000000」でメモリ操作を行うとssram1とssram2を連結した16MWのメモリとしてアクセスする事も可能です。

これは、USBコントローラ(FX2)とGPIF-AVALONブリッジ・マスタ内に各々2,048バイトのFIFOを持っているためです。

また、余分にリードした4096バイトはメモリリードが完了した時点で破棄してしまいますので注意して下さい。