検索

Contact

FPGAからAD/DA制御

FPGAからADC/DACをSPIで制御する場合の注意点

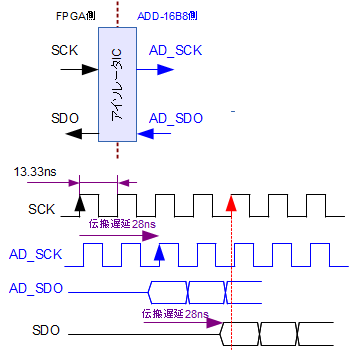

FPGAボード(CX-Card4/SX-Card6/AX-Card7)とADD-16B8間には、アイソレータIC(iCOUPLER)を採用しています。アナログデバイセズ社のADuM440xです。 このICは75MHzのクロック信号を通過できますが、伝搬遅延が大きくなります。

※2017.11以降出荷製品では、ADum440xの代替品としてADum14xを使用しています。

データシートでは、20nsから36nsの伝搬遅延が発生すると記載されています。ADコンバータIC(AD7980B)をSPI=75MHzで制御する場合、最悪3クロック弱分の伝搬遅延が発生することになります。

※2017.11以降出荷分から、伝搬遅延4.8ns~14ns(Typ.6.8ns)です。約1クロックの遅延です。

このため、FPGA側制御回路では伝搬遅延量を考慮した設計が必要になります。 伝搬遅延量はおおよそ28ns前後の製品が多いので、28nsを伝搬遅延量と仮定すると、以下の信号遅延が発生します。

※2017.11以降出荷分から伝搬遅延は約6ns~7nsです。

FPGAからSCK(75MHz)をADコンバータに出力すると、実際には28ns後にADコンバータに入力されます。ADコンバータはこの伝搬遅延が含まれたSCK(図ではAD_SCK)を元に変換動作を行い、変換出力のAD_SDO信号をFPGAに出力します。このときにも、実際にFPGAに到達するのは28ns後になります。

すなわち、FPGA側回路では、SCKを出力すると、約56ns後に変換データを受信できることになります。75MHz 4クロック分データが遅れていることにります。

※2017.11以降出荷分では、75MHzクロック1個分の遅延になります。