検索

Contact

FPGAのCRCエラー表示機能

SX-USB3搭載のStratix3デバイスは、SEU緩和機能(CRCエラー機能)を内蔵しているので、予期せぬコンフィグデータのエラーを防ぎます。

Stratix3デバイスは、SEU緩和機能(CRC機能)を内蔵しています。SEU緩和については、以下URLを参照してください。

http://www.altera.co.jp/products/devices/stratix-fpgas/stratix/stratix/features/stx-seu.html

FPGAにコンフィグされたデータに異常を認めると、FPGAはCRCエラーとして特定のIOピンをアクティブにします。SX-USB3は、ボード上でこの信号を検出し、使用者にLEDの点滅でお知らせします。

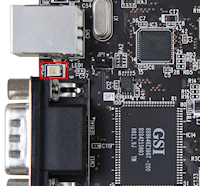

赤枠で囲んだLEDが赤点滅します。

通常、正常にFPGAコンフィグが行われると、緑点灯します。ボード運用中にFPGAコンフィグデータに異常が発生すると、赤点滅してお知らせします。

(注意) SX-USB3ボードでは、FPGA回路をQuartusIIでコンパイルする際に、CRCエラーチェック機能をアクティブにしないと、LEDが赤点滅します。

CRCエラーチェック機能をアクティブにしても、FPGAユーザ回路には動作的に影響を与えないので、機能をアクティブにすることをお勧めします。製品に添付するサンプル回路で使用しているスクリプトファイル(xxx.tcl)を利用すると簡単に設定できます。

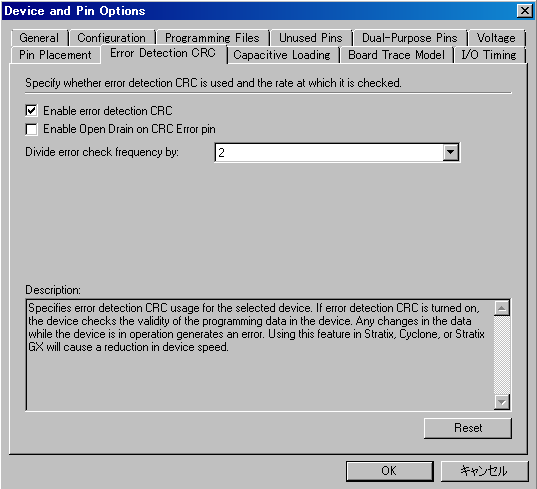

QuartusIIでの設定方法は、”Device and Pin Option"メニューの"Error Detection CRC"タブで、チェックボックスにチェックを入れるだけです。